1、以太網接口介紹:

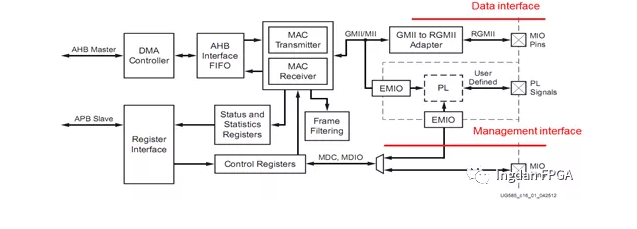

以太網接口包含管理(lǐ)、數據通信接口,管理(lǐ)接口也就是我們常說的MDC/MDIO,用(yòng)來訪問phy寄存器,配置工(gōng)作(zuò)模式、檢測工(gōng)作(zuò)狀态。數據接口:常見的有(yǒu)MII, GMII, RGMII,SGMII, QSGMII等,我們本次專注在RGMII。

TX/RX data between MAC & PHY

幀格式: CL22(GE), CL45(XE);

Preamble (32bits) | Start (2bits) | OP Code (2bits) | PHYAD (5bits) | REGAD (5bits) | Turn Around (2bits) | Data (16bits) | Idle | |

Read | 1.......1 | 01 | 10 | A4A3A2A1A0 | R4R3R2R1R0 | Z0 | D15.......D0 | Z* |

Write | 1.......1 | 01 | 01 | A4A3A2A1A0 | R4R3R2R1R0 | 10 | D15.......D0 | Z* |

RGMII規範中(zhōng)約定data和clock之間需要有(yǒu)2ns延遲,實現方式:

A. PCB闆上繞線(xiàn)實現 (不推薦);

B. PCB(data/clock等長(cháng)處理(lǐ))+PHY芯片上分(fēn)别設置TX/RX delay(現在phy基本上均支持,使用(yòng)前請查看phy手冊确認);

RGMII規範約定:

帶有(yǒu)internal delay的phy/mac:

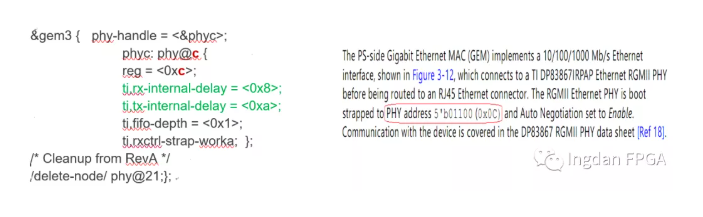

Linux如何配置phy地址&phy delay,以ZCU102為(wèi)例,GEM3 phy address=0xC,采用(yòng)phy internal tx/rx delay,在設備樹system-usr.dsti中(zhōng)添加phy地址和delay(有(yǒu)的phy硬件配置好,無需額外添加)。

5

在uboot下通過mii命令查看phy的link/AN/Speed狀态,或者配置loopback測試。

常用(yòng)命令有(yǒu)mii info、mii dump、miiwrite等等。

通過mii info可(kě)以查看MDC/MDIO總線(xiàn)下挂載了哪些phy address。

(8000:0000) 0.15 = 0 reset

更多(duō)問題,請聯系我們的FAE

simonyang@comtech.com.cn

深圳市科(kē)通技(jì )術股份有(yǒu)限公(gōng)司 客服電(diàn)話:(+86)755-26018083 郵箱:cs@comtech.cn

© Copyright 2018 www.comtech.cn | 京ICP證000000号 |  粵公(gōng)網安(ān)備 44030502003347号

粵公(gōng)網安(ān)備 44030502003347号